SAYISAL EVİRİCİLER

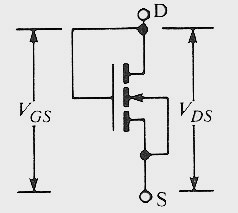

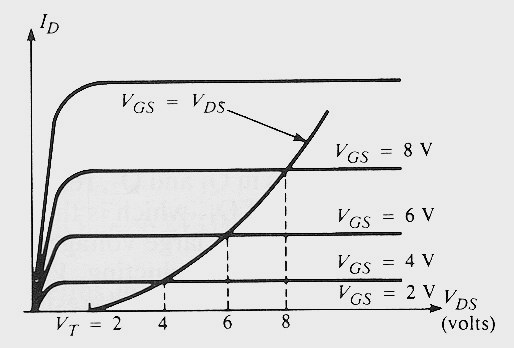

MOSFET eviriciler entegre devre yapımında geniş bir kullanım alanına sahiptir. Bilindiği gibi bir entegre devre tasarımında direnç yerine transistör yapmak daha kolay ve daha etkilidir. Bu nedenle MOSFET eviriciler entegre devre yapımında kullanılacakları zaman eviricinin yükünü oluşturacak devre bileşeni de MOSFET olarak seçilir. Diğer bir ifadeyle MOSFET'ler entegre devre yapımında yük olarak kullanılacakları zaman dirençlerin görevini üstlenirler. Şekil-4.1'de bir direnç olarak bağlanmış bir N-MOSFET gösterilmiştir. Dikkat edileceği gibi drain ile gate doğrudan bağlanmışlardır. Bu durumda VDS = VGS olmaktadır. Şekil-4.2'de bir NMOS drain karakteristiği üzerine kurulmuş VG = VDS eğrisi gösterilmektedir. Eğimin doğrusal olmadığına dikkat edin. Bu durum MOSFET'in doğrusal olmayan bir direnç gibi davrandığını gösterir. VGS = VDS = doğrusal olmayan direnç üzerindeki V gerilimi olduğundan, I-V karakteristik eğrisi denklemi I nolu denklemde görüldüğü gibi olur.

Örnek uygulama apletinde bir MOSFET'in evirici olarak kullanılması canlandırılmıştır. Apletten de görüleceği gibi yük bileşeni olarak yine bir MOSFET kullanılmıştır. Aplette MOSFET 2'nin yük eğrisi ve MOSFET 1'in drain karakteristiği de gösterilmektedir. Burada kontrol paneli butonuna tıklanmak suretiyle ekrana gelen kontrol penceresinden MOSFET'lerin beta değerleri değiştirilmektedir. Böylece devre girişi VDD-VT olduğunda beta değerlerinin VOL (alçak çıkış seviyesi) değerini nasıl etkiledikleri görülmektedir. Her voltaj seviyesi farklı renklerle gösterilmiştir. VOH = VDD-VT kadar olduğundan VCC'nin renginden biraz daha farklı renkle gösterilmiştir. Yine aynı şekilde VOL değeri tam olarak 0 olmadığından GND'nin renginden farklı bir renkle gösterilmiştir. Devrenin çalışma prensibi BJT eviricilerde olduğu gibidir. MOSFET (Q1) gerilim kontrollü anahtar gibi çalışır. Prensipteki fark burada BJT eviricilerde kullanılan sabit direnç yerine doğrusal olmayan direnç etkisine sahip başka bir MOSFET kullanılmıştır. VGS1 = VDD - VT olduğu durumda çıkış alçak seviyesi VON'u tespit etmek için aşağıdaki yöntem izlenir: VDS2 = VGS2 olduğuna dikkat edin. VDD ucundan GND'ye kadar Kirchoff'un gerilim kanununu yazacak olursak VDD = VGS2 + VON veya VGS2 = VDD - VON olduğunu görürüz. Böylece,

|

|||||||||||||||